发干货福利啦!别错过这些技术类的晶振问答

常常有客户或者工程咨询一些与石英晶体谐振器和振荡器相关的技术知识,尤其关于电路匹配,输出逻辑,测试项目,焊接条件注意事项和故障停振等相关内容,以便更了解晶振才更好运用,这些问题大部分在网络上是查不到的.因此康华尔电子特意整理一些,入门级并可以帮助工程师们了解晶振的问题,以及相关的答案,采用问答的方式,更好的吸引知识,为了感谢广大用户对我司十几年来的支持和信任,是时候来发点技术干货福利啦,走过路过千万不要错过哦!

一、为什么TCXO会剪切正弦波输出?

大多数陶瓷LCC封装的TCXO振荡器仅适用于削波正弦波输出.这样做有很多原因,尽管它让许多想要CMOS输出电平的电路设计者感到沮丧.CMOS输出会为TCXOIC增加显着的功耗.IC和封装中产生的温度梯度将限制实现最佳TCXO补偿的能力.各种可能的CMOS负载会改变补偿设计,因为内部热梯度会导致TCXO不符合规格.当输出电平变化时,CMOS输出会导致电源和接地瞬变.这种噪声会对TCXO的相位噪声性能产生不利影响.

CMOS输出晶振可以输出产生更大的EMI/RFI信号,这可能导致难以满足美国FCC和其他国家从最终系统辐射能量限制的困难.截断的正弦波既是低振幅又大部分是正弦波,导致低信号电平和较少的谐波.*使用这些TCXO的许多应用都具有ASIC输入,可接受限幅正弦波并在内部转换为CMOS逻辑电平.

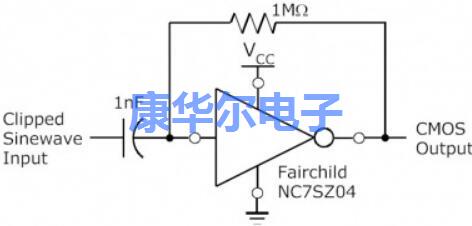

二、将削波的正弦波输出转换为CMOS

来自许多TCXO和其他振荡器的限幅正弦波输出信号很容易转换为CMOS输出信号.这个简单的电路可以由额定为0.8VPP限幅正弦波输出的振荡器驱动,规定最大负载为10K欧姆,与10pF并联.输出的CMOS方波具有VccPP电平,占空比接近50%.该电路工作电压范围为1.65V至5.5V,电源电压最低时为70MHz.将限幅正弦波转换为CMOS的成本很低.例如,2009年3月,一家全国知名的石英晶振产品分销商以5K的数量将Fairchild逻辑门列为0.052美元ea.Fairchild逻辑门采用SOT23-5和SC70-5封装.其他组件总价不到0.01美元.

三、精细泄漏测试标准

测试条件:

氦爆炸浸泡时间:7200秒(2小时)

轰炸压力:75psig

拒绝标准:

>5.00-8atm.cc/sec

四、为什么水晶的频率限制较低?

晶体的厚度决定了频率.对于AT切割晶体,0.001“(0.0254mm)厚度约为63MHz基模谐振器.如果厚度加倍,则谐振频率将为0.5*63MHz或31.5MHz.8MHz贴片晶振厚度为0.0078’(0.200mm).4MHz晶体厚度为0.0157’(0.400mm).遇到两个限制特定包装尺寸中最低频率的条件:

1)简单的条件,较新的薄型陶瓷LCC封装不接受较厚的晶体.根据封装,频率下限范围从8MHz到12MHz,向下.

2)请记住,石英晶体是一种振动机械装置.对于最佳设计,那些具有较低ESR(CI)和无扰动(引起频率跳跃的不希望的振动模式)的振动区域应位于晶体的中心区域.

当晶体频率较低且晶体较厚时,振动区域更加机械地耦合到边缘.在这种情况下,扰动(不需要的共振)变得难以控制.解决方案是使水晶倾斜或勾勒出轮廓(使水晶看起来更像放大镜的凹形).边缘的这种变薄将振动区域限制在晶体中心并允许控制扰动.

不幸的是,限制振动区域会显着增加ESR.例如在12MHz:

SM13T5x7mm晶振ESR最大值为50欧姆

SM11T3.2x5mm晶体ESR最大值为80欧姆

对于这个例子,低于12MHz的SM11T不实用,因为ESR变得非常大.

五、确定性抖动

可预测的抖动分量称为确定性抖动.对于非倍增石英晶体振荡器,确定性抖动通常小于0.01pS.

六、冲击水平和破碎的晶体导致故障

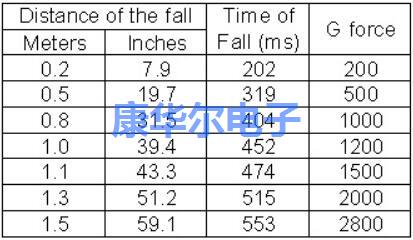

石英晶体和有源晶振最常见的故障之一是破碎的晶体.包装内的晶体悬浮在包装内的自由空间中,悬浮在干燥的氮气中或抽空的空间中.高冲击会导致精密定时元件断裂.大多数Pletronics产品的额定功率为1500Gs,通过将设备放在地板上可以轻松达到这种水平的冲击.该图表显示了将物体放在硬木或乙烯基型地板表面上时达到的G力.混凝土地板上的力要高得多.

七、总抖动

总抖动是确定性抖动和随机抖动的总和,对于非倍增晶体振荡器(使用基模或第三谐波谐振器的振荡器),确定性抖动通常小于0.01pS.

八、建议PCB/PWB焊盘几何形状

随着无铅处理和RoHS的到来,Pletronics停止推荐晶体和振荡器的焊盘设计.以前整个电子行业都在使用铅锡焊料,而Pletronics可以根据这一一致性要求提出建议.今天,我们有许多不同的工艺,许多不同的助焊剂,许多不同的工艺温度.再加上这种复杂性,人们担心焊点会产生化学成分.例如,我们的陶瓷晶体和振荡器在镍焊盘上镀金以确保可焊性,对于一些最终用户而言,担心在完成的焊点中产生的金浓度.最终用户必须在考虑Pletronics晶振焊盘,PCB/PWB焊盘尺寸,PCB/PWB上的任何镀层和焊接屏幕厚度的同时,决定使其工艺可靠地运行的原因.Pletronics确实在数据表上提供准确的封装焊盘信息,以帮助确定正确的PCB/PWB设计.